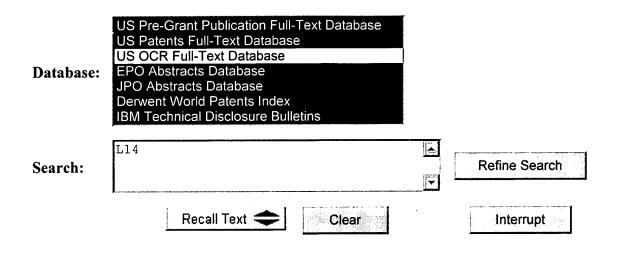

# **Refine Search**

#### Search Results -

| Terms            | Documents |

|------------------|-----------|

| key with address | 21815     |

### **Search History**

## DATE: Friday, February 11, 2005 Printable Copy Create Case

| Set Name<br>side by side                               | Query                      | Hit Count | Set Name result set |  |  |

|--------------------------------------------------------|----------------------------|-----------|---------------------|--|--|

| DB=PGPB, USPT, EPAB, JPAB, DWPI, TDBD; PLUR=YES; OP=OR |                            |           |                     |  |  |

| <u>L14</u>                                             | key with address           | 21815     | <u>L14</u>          |  |  |

| <u>L13</u>                                             | 13 with L12                | 82        | <u>L13</u>          |  |  |

| <u>L12</u>                                             | l4 with processor          | 2050      | <u>L12</u>          |  |  |

| DB=USPT; PLUR=YES; OP=OR                               |                            |           |                     |  |  |

| <u>L11</u>                                             | partition\$ adj2 processor | 511       | <u>L11</u>          |  |  |

| <u>L10</u>                                             | 16                         | 34        | <u>L10</u>          |  |  |

| <u>L9</u>                                              | 14                         | 15898     | <u>L9</u>           |  |  |

| DB=PGPB, USPT, EPAB, JPAB, DWPI, TDBD; PLUR=YES; OP=OR |                            |           |                     |  |  |

| <u>L8</u>                                              | 15 and 16                  | 13        | <u>L8</u>           |  |  |

| <u>L7</u>                                              | 12 with 15                 | 416       | <u>L7</u>           |  |  |

| <u>L6</u>                                              | 12 with 14                 | 74        | <u>L6</u>           |  |  |

| <u>L5</u>                                              | partition\$                | 411042    | <u>L5</u>           |  |  |

| <u>L4</u>                                              | memory adj2 (map or table) | 25508     | <u>L4</u>           |  |  |

| <u>L3</u>                                              | rout\$                     | 753516    | <u>L3</u>           |  |  |

| <u>L2</u>                                              | router                     | 60951     | <u>L2</u>           |  |  |

| <u>L1</u>                                              | 6247109.pn.                | 2         | <u>L1</u>           |  |  |

|                                                        |                            |           |                     |  |  |

Welcome **United States Patent and Trademark Office**

| Help  | FAQ     | Terms   | IEE  |

|-------|---------|---------|------|

| Welco | me to l | EEE Xpl | oree |

E Peer Review

**Quick Links** •

| Welcome to | IEEE Xplore® |

|------------|--------------|

|            |              |

- Home

What Can I Access?

O- Log-out

#### Tables of Contents

) - Journals & Magazines

( )- Conference **Proceedings**

( )- Standards

#### Search

( )- By Author

O- Basic

O- Advanced CrossRef

# Member Services

()- Join IEEE

O- Establish IEEE **Web Account**

Access the **IEEE Member** Digital Library

#### TEEE Enterprise

Access the **IEEE Enterprise** File Cabinet

Print Format

Your search matched 12 of 1124699 documents.

A maximum of **500** results are displayed, **15** to a page, sorted by **Relevance** in **Descending** order.

#### **Refine This Search:**

You may refine your search by editing the current search expression or entering a new one in the text box.

router <and> memory <and> mapping

Search

Check to search within this result set

#### **Results Key:**

JNL = Journal or Magazine CNF = Conference STD = Standard

## 1 An architecture based on the memory mapped node addressing in reconfigurable interconnection network

Ikedo, T.; Yamada, J.; Nonoyama, Y.; Kimura, J.; Yoshida, M.; Parallel Algorithms/Architecture Synthesis, 1997. Proceedings. Second Aizu International Symposium, 17-21 March 1997 Pages:50 - 57

[Abstract] [PDF Full-Text (816 KB)] **IEEE CNF**

#### 2 A scalable cache coherent scheme exploiting wormhole routing networks Yunseok Rhee; Joonwon Lee;

High-Performance Computer Architecture, 1999. Proceedings. Fifth International Symposium On, 9-13 Jan. 1999

Pages: 223 - 226

[Abstract] [PDF Full-Text (92 KB)] **IEEE CNF**

## 3 EMPOWER: a cluster architecture supporting network emulation

Pei Zheng; Ni, L.M.;

Parallel and Distributed Systems, IEEE Transactions on , Volume: 15 , Issue: 7 , July 2004

Pages:617 - 629

[Abstract] [PDF Full-Text (1200 KB)] **IEEE JNL**

### 4 A high-performance architecture and BDD-based synthesis methodology for packet classification

Prakash, A.; Kotla, R.; Mandal, T.; Aziz, A.;

Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions

on , Volume: 22 , Issue: 6 , June 2003

Pages: 698 - 709

[Abstract] [PDF Full-Text (474 KB)] **IEEE JNL**

5 Reconfigurable finite-state machine based IP lookup engine for highspeed router

Desai, M.; Gupta, R.; Karandikar, A.; Saxena, K.; Samant, V.;

Selected Areas in Communications, IEEE Journal on , Volume: 21 , Issue: 4 , May 2003

Pages: 501 - 512

[Abstract] [PDF Full-Text (825 KB)] IEEE JNL

# 6 A priority-driven flow control mechanism for real-time traffic in multiprocessor networks

Balakrishnan, S.; Ozguner, F.;

Parallel and Distributed Systems, IEEE Transactions on , Volume: 9 , Issue: 7 , July 1998

Pages:664 - 678

[Abstract] [PDF Full-Text (852 KB)] IEEE JNL

#### 7 A flexible bit-pattern associative router for interconnection networks

Summerville, D.H.; Delgado-Frias, J.G.; Vassiliadis, S.;

Parallel and Distributed Systems, IEEE Transactions on , Volume: 7 , Issue: 5 , May 1996

Pages: 477 - 485

[Abstract] [PDF Full-Text (936 KB)] IEEE JNL

# 8 Performance analysis of multi-dimensional packet classification on programmable network processors

Srinivasan, D.; Wu-chang Feng;

Local Computer Networks, 2004. 29th Annual IEEE International Conference on , 16-18 Nov. 2004

Pages: 360 - 367

[Abstract] [PDF Full-Text (184 KB)] IEEE CNF

#### 9 High-performance IP routing table lookup using CPU caching

Chiueh, T.; Pradhan, P.;

INFOCOM '99. Eighteenth Annual Joint Conference of the IEEE Computer and Communications Societies. Proceedings. IEEE , Volume: 3 , 21-25 March 1999 Pages:1421 - 1428 vol.3

[Abstract] [PDF Full-Text (808 KB)] IEEE CNF

#### 10 Incremental routing in FPGAs

Emmert, J.M.; Bhatia, D.;

ASIC Conference 1998. Proceedings. Eleventh Annual IEEE International , 13-16 Sept. 1998

Pages:217 - 221

[Abstract] [PDF Full-Text (448 KB)] IEEE CNF

#### 11 FPGA-based Internet Protocol Version 6 router

Mansour, M.; Kayssi, A.;

Computer Design: VLSI in Computers and Processors, 1998. ICCD '98.

Proceedings., International Conference on , 5-7 Oct. 1998

Pages: 334 - 339

[Abstract] [PDF Full-Text (64 KB)] IEEE CNF

# 12 An empirical study of datapath, memory hierarchy, and network in SIMD array architectures

Herbordt, M.C.; Weems, C.C.;

Computer Design: VLSI in Computers and Processors, 1995. ICCD '95. Proceedings., 1995 IEEE International Conference on , 2-4 Oct. 1995

Pages:546 - 551

[Abstract] [PDF Full-Text (580 KB)] IEEE CNF

Home | Log-out | Journals | Conference Proceedings | Standards | Search by Author | Basic Search | Advanced Search | Join IEEE | Web Account | New this week | O Linking Information | Your Feedback | Technical Support | Email Alerting | No Robots Please | Release Notes | IEEE Online Publications | Help | FAQ| Terms | Back to

Copyright © 2004 IEEE — All rights reserved